38 prominent partners

DARE brings together 38 prominent partners from across Europe, including ICSC – National Research Center in HPC, Big Data and Quantum Computing, the lead of a consortium that also includes the Universities of Turin, Pisa, and Sapienza University of Rome, the Polytechnics of Turin and Milan, the International School for Advanced Studies (SISSA) of Trieste, and the National Institute for Nuclear Physics (INFN). With a budget of 240 million euros, the initial phase of the project, lasting three years, will lay the foundations for the continuation of the DARE initiative over the following three years, whose goal will be to provide Europe with innovative high-performance and energy-efficient processors optimized for HPC and AI, capable of ensuring European sovereignty and independence in a technological sector that has become of fundamental strategic importance.

The project partners

To achieve this goal, the project partners will operate in a coordinated manner, leveraging as a basis for their research and development activities open hardware architecture standards already available, such as RISC-V, and the most advanced technologies for creating microprocessors called chiplets, capable of integrating the different systems involved in computation into the same substrate, in order to create fully European products that will power future supercomputers. “I am proud to announce the launch of the DARE project, which marks a milestone for European digital sovereignty. This ambitious initiative will promote innovation in hardware and software technologies, harnessing the full potential of HPC and AI to develop secure, efficient, and Europe-driven solutions for the future,” declared Anders Jensen, Executive Director of EuroHPC JU.

DARE

Thanks to DARE, Europe, still today a simple consumer of external hardware and software solutions, intends to ensure its independence in the production of microprocessors and algorithms for HPC and Artificial Intelligence, a factor that will allow it to avoid risks related to security, economic stability, and technological competitiveness associated with sourcing from third countries.

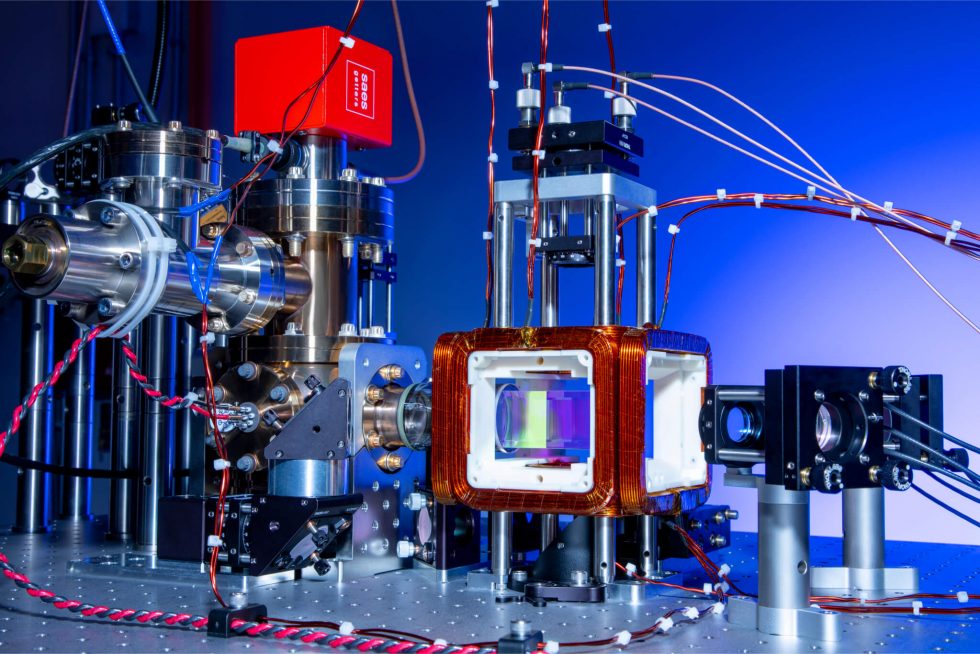

At the heart of the DARE SGA1 project is the development of three chiplets based on RISC-V, each playing a crucial role in HPC and AI:

- Vector Accelerator (VEC) for high-precision HPC calculations and emerging applications in HPC-AI convergence, led by Openchip

- AI Processing Unit (AIPU) designed for AI inference acceleration in HPC applications, led by Axelera AI

- General-Purpose Processor (GPP) optimized for HPC workloads in European supercomputers, led by Codasip

These chiplets will be developed and manufactured with advanced technology nodes, overcoming the limitations of traditional monolithic chips and offering greater efficiency, scalability, and cost advantages.

Co-design between hardware and software

To ensure the success of these innovations, DARE SGA1 will adopt a hardware-software co-design approach, using a selected set of European HPC and AI applications to guide development. In parallel with hardware design, a comprehensive software ecosystem will be created to simplify the transition to the new RISC-V processors for application users. The project will also include exploratory activities for futuristic HW and SW design and scalability studies for the next generations of supercomputers.

“The Italian research ecosystem in the HPC field,” emphasized Marco Aldinucci, PI for the ICSC National Center in DARE, “has the necessary expertise to play an important role in DARE. These are rare skills in Europe, ranging from the design of programming tools (libraries, workflows, compilers, energy monitoring systems), to the design and verification of hardware and inter-chip network protocols, to applications that have become reference points for the HPC area, such as QuantumEspresso. These skills, distributed across several universities and research institutions, together with the ICSC foundation reach the critical mass necessary to participate in a large-scale project like DARE.”

DARE SGA1 and the future of European HPC

At the end of its first phase, DARE SGA1 will lay the foundations for the first fully European HPC system, promoting technological self-sufficiency and ensuring that industry, research, and society can benefit from secure, high-performance, and energy-efficient solutions. The project, in fact, will not be limited to technological development, but will define the roadmap for European post-exascale supercomputers, paving the way for a new generation of supercomputers designed, built, and optimized in Europe, ensuring that the continent remains at the forefront in the development and use of HPC and AI.

“Being part of DARE SGA1 is an important recognition for ICSC, highlighting our role as a collaborative ecosystem in the European HPC landscape,” emphasizes Alessia D’Orazio, Research Manager at the ICSC Foundation, “ICSC is not just a research center, but a hub for various stakeholders, from universities to companies, all united by the common goal of developing cutting-edge HPC technologies, particularly through Spoke 1 ‘Future HPC & Big Data’. Participation in DARE strengthens this vision, allowing us to coordinate the expertise and resources of a wide network of partners. Together, we work to create innovative solutions that will power future European supercomputers, ensuring the continent’s technological sovereignty. The synergy among our partners and alignment with DARE’s objectives allows us to maximize the impact of our research, consolidating our position as a reference actor in the European HPC sector.”

Among the 38 European partners of DARE, together with ICSC and the consortium members coordinated by the National Center, the Italian team is represented by CINECA, University of Bologna, AXE-IT, and E4.